Good afternoon,

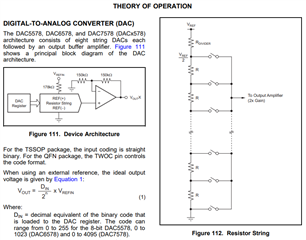

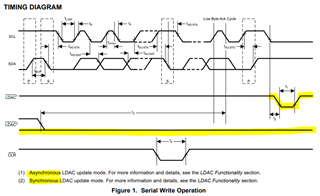

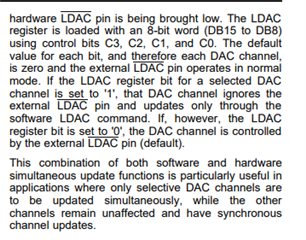

Overall question: Do I need to map pins 1 or 8 to anything? Do i need to provide the DAC with any other commands to possibly shift its input from the data buffer to the register? Do I need to further power on the DACs beyond just applying a voltage to AVDD and connecting GND to the appropriate pins?

I'm wondering whether there are additional steps i need to take IOT have the DAC6578 operate correctly. I'm following along with Ex1 on p40 of the data sheet.

-ive verified that each of the necessary commands is making it to the I2C bus and the dac is acknowledging the commands (i2c SDA pulled low at 9th bit position)

-I am using the TSSOP package.

-i have 3v3 applied to pin 3 (AVDD)

-pin 1 (LDACn) and pin 8 (Vrefin) are floating.

My understanding is that i will automatically see 1.65V on pin4 (Vout_A) since i am writing midscale to register A (exactly like the above example) and my voltage range is from 0 to 3v3. are my expectations off?

as an aside, what does it mead to "load a dac"?