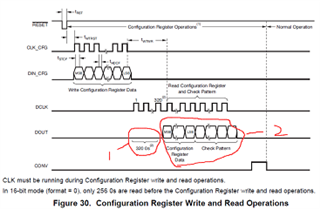

What is the 320 0s mean in the circle one?

What is the readback data strructure after Configuration Register Data Write and 320 DCLK Clock Pulses Provied in the circle two?

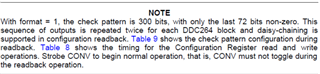

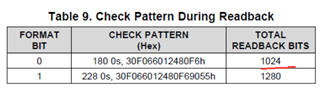

According to the NOTE and Table 9,16bits Configuration Resgister Data,then 4-bit revision ID,and 300bits the check pattern,how can it has 1024 TOTAL READBACK BITS with format = 0 ?

And what is the 4-bit revision ID,how can i set them?

Thanks for your help!