The ADS7881 Specification, regarding the readout of the digitized data: The time for the DATA to be enabled onto the bus (td6) is 25ns maximum. The time for the DATA to decay from a disable (READ deasserts) is also 25ns (td9).

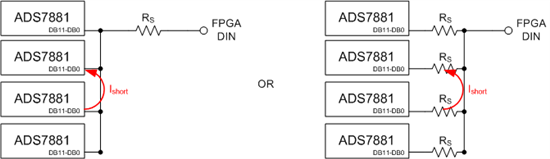

I have a group of these converters tied together on the same DATA bus. I'd like to disable the first and then enable the second, and gain some setup time before reading out the second one. If I enable the second 7881 10ns following the deassertion of READ on another 7881, would this cause any damage? (One ICs data is still decaying, when the second IC gets its enable.) I wouldn't sample during this period, just want to get a headstart by asserting READ a little bit earlier.