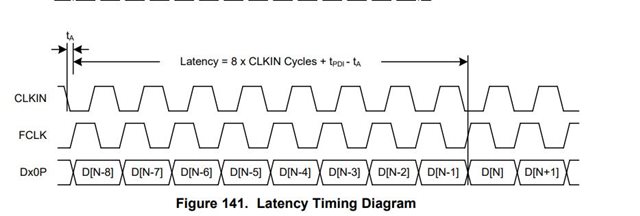

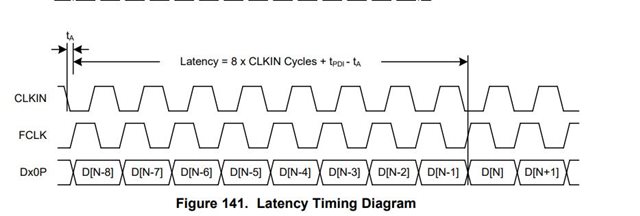

Are the sampling of the 4 channels synchronized? From this timing chart, does the output data appear to be out of sync? Latency=8 x CLKIN Cycles+tPDI - tA, what does this delay time refer to?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Are the sampling of the 4 channels synchronized? From this timing chart, does the output data appear to be out of sync? Latency=8 x CLKIN Cycles+tPDI - tA, what does this delay time refer to?

Hi Zhang,

The sampling of the 4 channels is synchronized. If you look at the timing diagram in the datasheet that is in the middle of Figure 141, you can see that for one cycle of the FCLK a single data sample is captured. ADC latency is the time that it takes the device to sampling the input signal and convert it to a digital binary word at the output. The equation for latency, as you mentioned -> Latency=8 x CLKIN Cycles+tPDI - tA, describes the latency for the entire chip. Several factors contribute to latency, i.e., tPDI (clock propagation delay); tA (aperture delay).

Regards, Amy

Hi Zhang,

The ADC3441 has a minimum sampling rate of 15M, this cannot be lowered.

Regards, Amy