I am using the ADS1262 for high precision acquisition, the reference voltage is using the ADR4550, and the test signal source is using a 18650 lithium battery(4V ). Using the highest 2.5SPS sin4 mode, the code noise is about 21~22-bit stable. If you switch directly to AVDD + AVSS, the data noise can be about 23~24bit.

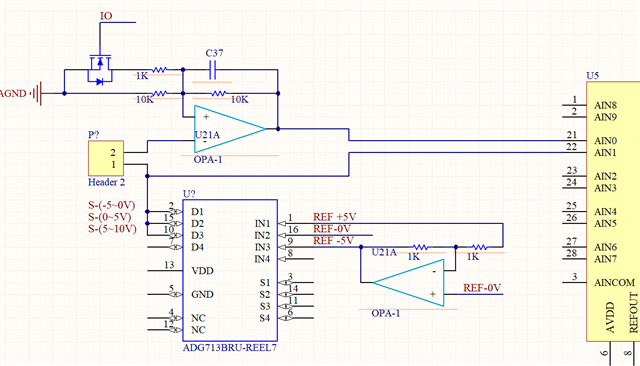

When using the reference voltage, 1k+10uF is used for RC filtering to reduce the reference input noise. (The voltage drop caused by the 10K resistor is ignored for now.) The signal is increased from 21~22bit to about 23bit. It shows that the reference voltage still contributes a lot to the code noise

As seen in the datasheet, up to 25 bits can be achieved (Noise Free Bits)。I want to know whether this parameter is conservative or theoretical. To achieve this performance, how low should the reference voltage noise and input noise be (? uVpp)

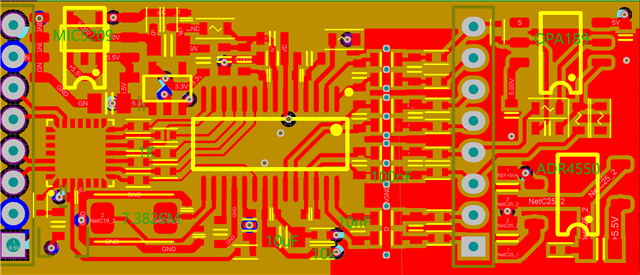

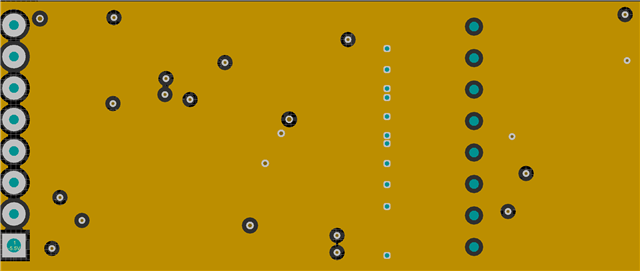

The reference layer only makes all-copper into the AGND and ensures that no current flows on it (except for the signal input capacitor filter current)

I want to get the nominal 25bit(The reading is noise-free), whether I can do it, I need to do those optimizations