Other Parts Discussed in Thread: ADC12DJ3200, LMK04828

Hi team

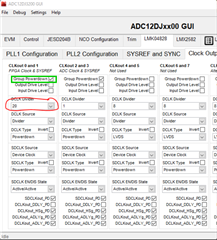

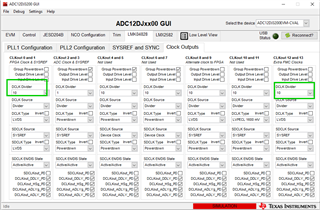

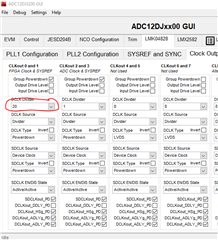

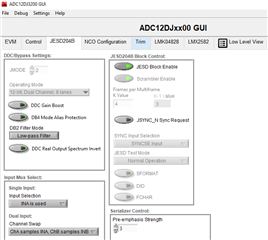

I am trying to interop ADC12DJ3200 with FPGA but the link (SYNC status) always stays low. I am supplying clocks to both FPGA and ADC through the clock oscillator on the ADC12DJ3200 EVM. I am using ADC12DJ3200 GUI for configuration of ADC and oscillator registers for clock. Since my target data rate is 10Gbps, I am setting Fs=2500 Msps in the GUI and using JMODE2. Also I want to supply 125 Mhz reference clock to FPGA for that I set the DCLK Divider value as 20 as shown below i.e 2500/20=125 Mhz but my link never goes up. I am sure this is the clock issue.

What am I doing wrong here? Any parameter I am setting wrong here? Anticipating a quick response on this.

-trs