Hi Team

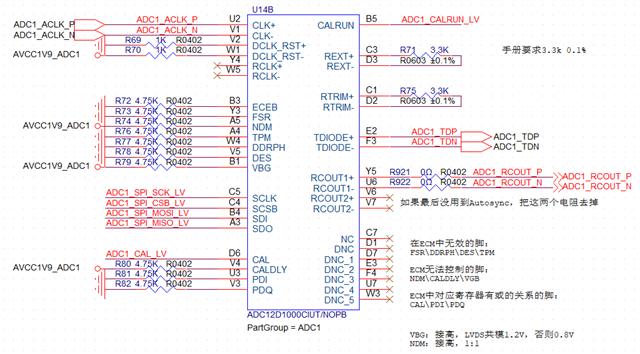

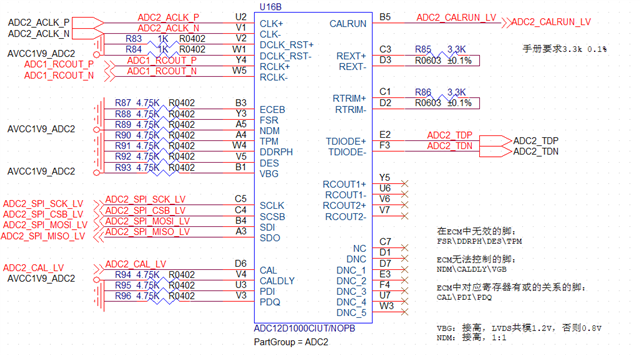

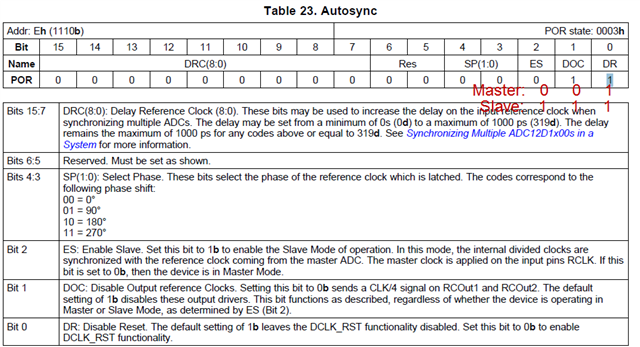

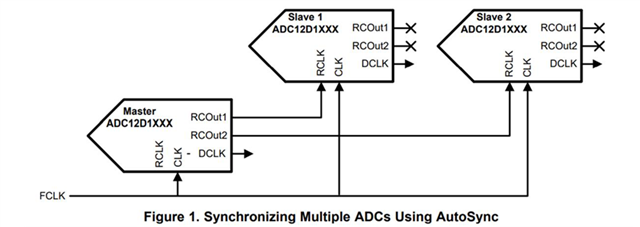

Customer wanna facilitate the autosync feature of ADC12D1000. they try to configure system depend on the following note. but can't works.

Can you show your insight that what kind of information that customer providing to help identify the root reason that doesn't works?

Thanks!