Hello All,

I'm using external reference and asynchronous update.

My setup is as follows:

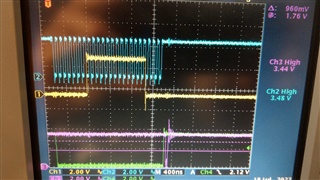

1 -Vout A - oscilloscope

2 -Vout B - oscilloscope

3 - GND

4 - LDAC - FPGA output

5 - CLR - tied to GND via 10k

6 - SYNC - FPGA CS output

7 - SCLK - FPGA SCLK

8 - DIN - FPGA DOUT

9 - Avdd - 5.0V (with appropriate bypass caps)

10 - Vrefin/Vrefout - tied to Avdd

Both outputs start with Avdd/2 = 2.5V

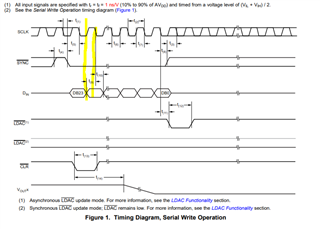

Signal timings as follows:

DAC gets updated on every command set , doesn't seem to be any timing issue. If I update output A with 0x00 0x00 0x00 it goes to 0V level. If I then send 0x00 0xFFF 0x00 to update output A , it only goes to ~ Vref/2. If I send 0x01 0x00 0x00 the Output B will not change (stays at Vref/2), but output A goes to max 5V level simultaneously.

I’m observing this behavior on two samples of DAC7563T . I tried other combination of command bits per Table 17 with same result (or no update for 001). The DAC is in asynchronous mode and is updated with LDAC going low, so my understanding I need command bits set to 000 and addresses for outA and outB to 000 and 001. I see it updates just fine but outputs a wrong analog levels and acts just like output B becoming a reference for output A.

Does the internal reference get enabled somehow, or I just have a output failure on both samples ?