Other Parts Discussed in Thread: ADS8883

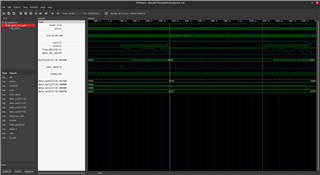

the ADS8881 has different modes. i wanted to use the "10.4.2.1 Daisy-Chain Mode Without a Busy Indicator" because it seems to be the easiest if You only want to connect one device per SPi-interface. there are only 3 signals used. and in the diagram "Figure 61. Interface Timing Diagram: For Two Devices in Daisy-Chain Mode" there is exactly 18 SCLK cycles used per device. i only have one device and would need 18 cycles. the problem is: the ADC gives me only 13 data bits. i have to add five additional clock cycles to get all the 18bits out.

the strange thing is: all SPi-modes whit DiN as chip select have some additional 5 SCLK cycles in the diagrams (Figure 53. Interface Timing Diagram: 3-Wire CS Mode With a Busy Indicator (DIN = 1) as example).

now i wonder: should i clock 18+5 cycles per ADC in the dasy-chain mode? or should i add some 5 clocks in the "converting time"? what is the reason of the 5 extra clocks in the SPi-modes?ads8881.pdf

help!!!