Other Parts Discussed in Thread: LMK00308, LMK04832

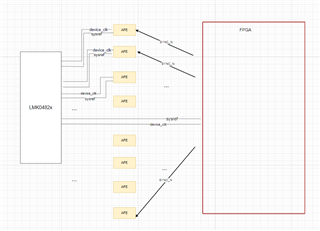

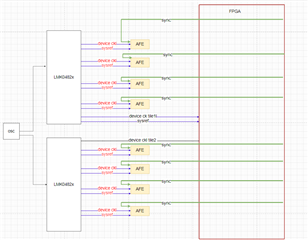

I use an FPGA to synchronously receive data from 8 AFEs through the JESD204B interface subclass 1, how should I connect the clock and sysref signal to the AFEs and FPGA? I found that the LMK0482X chip only supports a maximum of 7 pairs of device clocks and SYSREF outputs. I'm not sure if I need to connect 8 pairs of device clocks and SYSREF to the AFEs, and additionally connect 1 pair of device clock and SYSREF to the FPGA. If so, the output of one LMK0482X chip would not be enough. All my 8 AFEs are operating in the same mode.