Other Parts Discussed in Thread: TSW14J57EVM, ADC12DJ5200SE

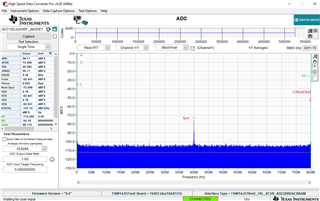

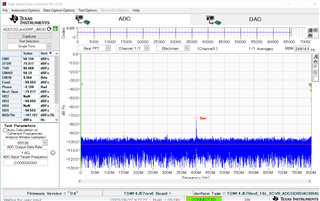

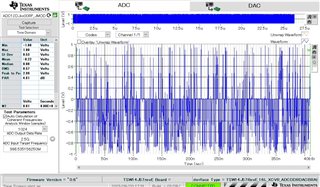

We couldn't capture appreciate data on "High Speed Data Converter Pro"(HSDC) with "TSW14J57EVM" and "ADC12DJ500SE EVM". Concretely, we input a 10MHz 1Vp-p sine wave but capture the waveform shown in the attached figure.

Could you please tell us some tips or suggestion on how to solve this problem? We describe the settings below.

TSW14J57EVM settings on HSDC

FPGA firmware: TSW14J57RevE_16L_XCVR_ADCBRAMDACDDR.rbf

ADC files: ADC12DJxx00RF_JMODE0.ini

ADC Output Data Rate: 2.5GHz

ADC Input Target Frequency: 998.53...MHz*

*We check "Auto Calculation of Coherent Frequencies".

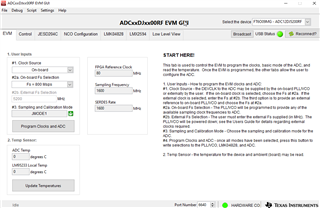

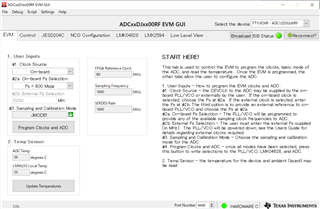

ADC12DJ500SE EVM settings on ADCxxDJxx00RF EVM GUI

"EVM" tab >> 1. User Inputs

#1 Clock Source: On-board *

#2 On-board Fs Selection: Fs = 5200Msps

#3 Sampling and Calibration Mode: JMODE0

*We fixed the part of circuits shown in Fig7-5 of "slau640b.pdf".