Hi there,

We found the risk of in-compatible voltage levels in the original post https://e2e.ti.com/support/data-converters-group/data-converters/f/data-converters-forum/1233289/afe5828-1v8-logic-input-voltage-level-compatibility-question/4661745?tisearch=e2e-sitesearch&keymatch=%25252525252525252520user%2525252525252525253A463167#4661745

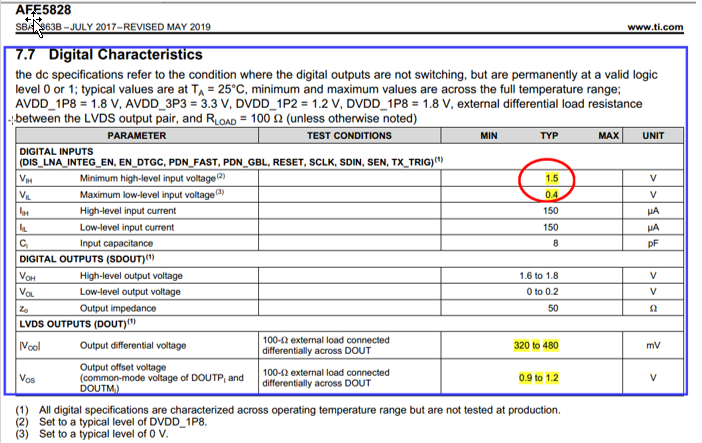

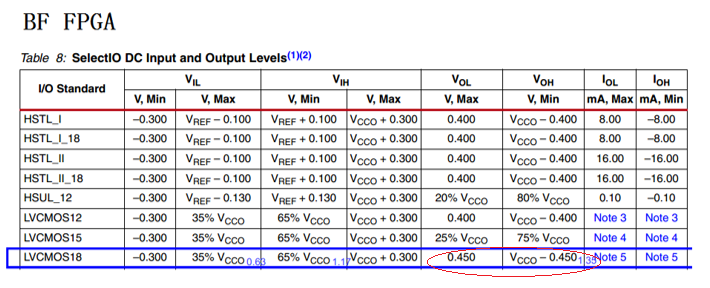

As the pic shows, FPGA's VoL(max 0.45V) > AFE's ViL(max 0.4V), and FPGA's VoH(min 1.35V) < AFE's ViH(min 1.5V). which means that AFE may not receive correct logic inputs under some boundary conditions.

1. Although we can insert a voltage level shifter to ensure they are compatible ( We do not want to do so actually, because we think the risk is low), but we are still confused : since both FPGA and AFE5828 claimed they are LVCMOS1.8V standard, they SHOULD be able to connect to each other directly without any risk.

2. May I ask what does the AFE5828 section 7.7 note(2)/(3) mean that "SET TO a typical level of xxx"? the typical level in the table is 1.5V and 0.4V.

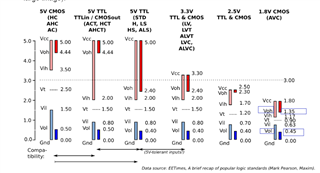

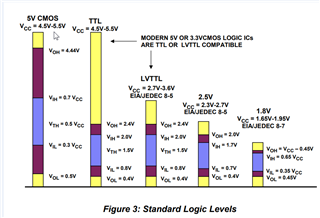

3. By the way, I searched on web, for LVCMOS1.8V, VOH=1.35V and VOL=0.45V. however, AFE5828 is different(stricter?, 1.5V and 0.4V.) . could you help explain this ?

https://www.jsykora.info/2014/05/logic-voltage-levels/

Thanks!