Hi team!

My customer is interested in this IC and has further questions about the noise spec.

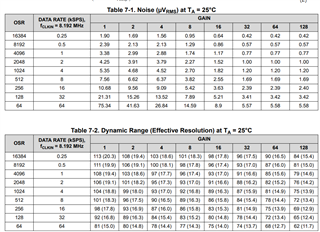

Below table is from page15. It is when the master clock is set at 8.192 MHz.

I understand that the modulation clock and the filter clock (mod clock/OSR) are critical parameter for the above noise values.

Q1. My customer needs the noise values & DR values when the2MHz, 1MHz, 300kHz. Do we have some values here? How one can calculate these values?

Q2. Can you tell us the mechanism and the relation ship of Noise and DR vs High-resolution mode/Low-power mode/VLP?

Thanks,

Luke