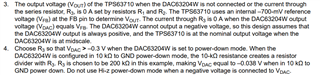

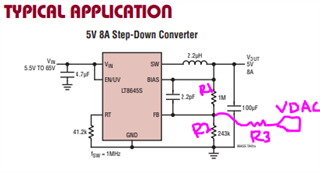

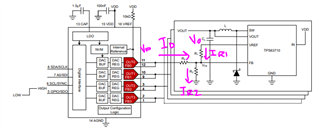

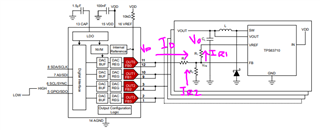

For a DC/DC circuit that outputs negative voltage, is it feasible to adjust the negative rail by changing the magnitude of the current from the source current of the DAC and passing it through the resistor between FB and VOUT, and finally injecting it into the negative rail?

The output of the DAC is generally about -1V relative to GND, does this violate the compliance voltage requirement of the DAC?