Hello TI Community,

I'm in the process of analyzing the AFE5816 chip for a planned design and have a few questions that I hope the community can help me with:

-

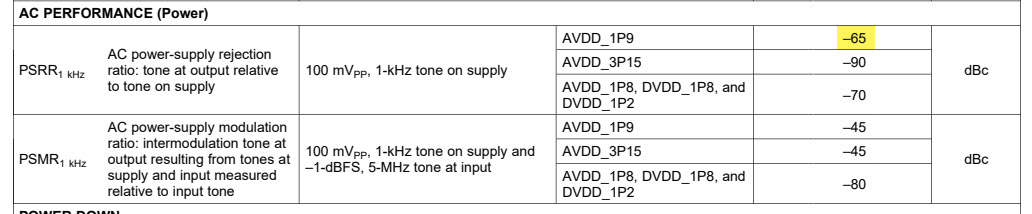

AC PERFORMANCE (Power) - AVDD_1P9 PSSR: I noticed in the AC PERFORMANCE (Power) section that the PSSR of AVDD_1P9 is -65, which seems lower than other supplies. Can someone elaborate on how noise on this supply might impact the sampling output of the chip? Additionally, any recommendations on PDN impedance or accepted ripple current for this supply would be greatly appreciated.

-

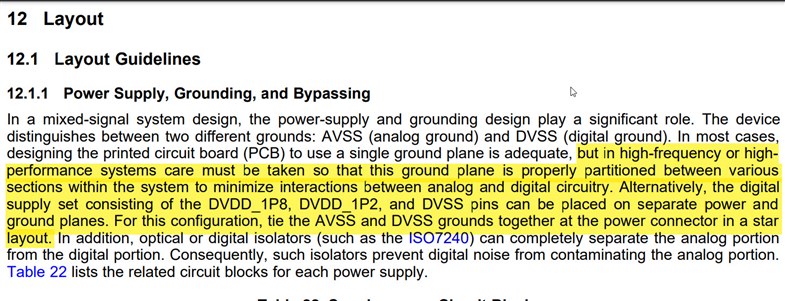

Digital Ground (DVSS) and Analog Ground (AVSS) Connection: I'm seeking clarification on whether DVSS and AVSS are internally connected. To control the return current of the analog inputs, understanding how to split the grounds is crucial. Considering that SPI is shared between two dies, if a buffer IC is needed for SPI signals, should it be DVSS-referred or AVSS-referred?

-

Board Layout - INPx and INMx Pins: In the "12.1.2 Board Layout" section, the recommended layout suggests isolating the INPx and INMx pin area by avoiding power planes under the INM and INP pins, and cutting the ground plane under these pins. I'm concerned about potential impedance mismatch and crosstalk. Can someone provide insights or suggest best practices to address these concerns?

-

AFE5816EVM Design or Fabrication Files: I'm planning to purchase the AFE5816EVM, but due to our design schedule, I'm wondering if there's a chance to access the design or fabrication files of the AFE5816EVM or any layout examples from the datasheet.

I appreciate any insights or guidance from the experienced members of the community. Thank you!