Other Parts Discussed in Thread: LMK04828

Hello,

We have a test platform with a DAC39J82EVM and a ZCU102 and see some activity on the JESD bus from the FPGA side but we don't see anything coming out of the DAC and the SYNC signal never changes.

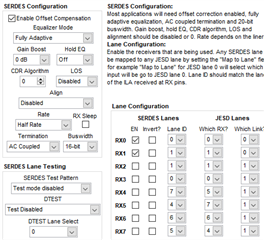

The Xilinx JESD IP on the FPGA is configured as a 2 lane link, with line speed of 6.144 Gbps and a reference clock of 307.2 MHz using CPLL.

We are using this clocking scheme on the FPGA from the JESD PHY datasheet:

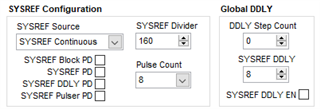

The LMK04828 on the TI board generates both, the 307.2 MHz CPLL ref clk and the 153.6 MHz core clk (1/40 line rate), both passed to the FPGA via the FMC connector. Right now we have SYSREF to be continuous.

We are using the GUI to program the TI board with these settings:

It seems we are not getting any alarms:

Yet, we don't see any output on the DAC.

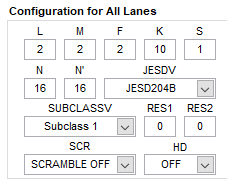

We are using this JESD configuration although we are not sure how to replicate that on the Xilinx JESD IP:

Any help would be greatly appreciated. We can provide more details if necessary.

Juan