Hello.

We are using a ZCU102 and DAC39J82EVM as a development platform for a project but we are not sure about what do some of the parameters mean.

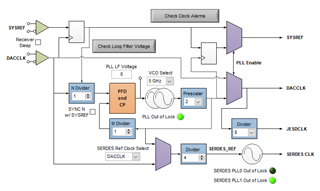

First, in the Clocking tab of the DAC3xJ8x controls: What is the difference between DACCLK, JESDCLK and SERDER CLK? Our DACCLK is 2.4576GHz and we are sending 307.2MSPS on 2 lanes with lane speed of 6.144Gbps.

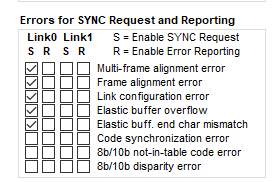

We also observe the SYNC signal goes low when we select either "Code synchronization error", "8b/10b not-in-table code error", or "8b/10b disparity error" from the SYNC request setting.

Is this more likely due to a misconfiguration on the FPGA side or the DAC side?

Thanks beforehand,

Juan