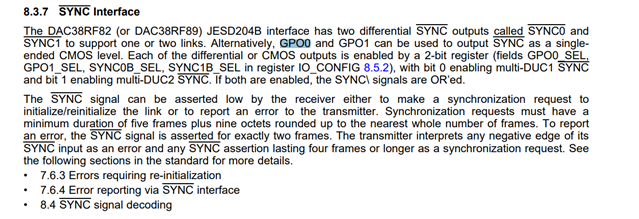

Other Parts Discussed in Thread: DAC38RF82,

DAC38RF82 The SYNC signal is high when it is powered on

I encountered a problem when debugging the DAC38RF82, as soon as the chip was powered on, it remained high without JESD204B link settings.

In the 204B protocol, the SYNC signal should be used by the receiver DAC to send a synchronization request, and the DAC should first set the SYNC low to send a synchronization request when it is powered on, and then pull the SYNC up after receiving the K code (BCBC) sent by the sender and completing the link synchronization. But now SYNC has been high since the power on, and it has not been pulled low even after configuring the register, is this a misconfiguration of the register or a problem with the chip hardware? Under what circumstances will SYNC be consistently high? The chip circuit board is DAC38RF82EVM.

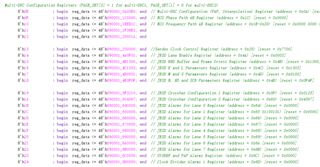

The clock circuit uses the On-Board VCXO Clock Mode (CMODE4) mode in the DAC38RF8xEVM to replace the VCXO of the board with 120MHz, change the register settings, the VCO frequency is 2.5GHz, the DACCLK+ frequency of the clock output to the DAC is 2.5GHz, and the SYSREF+ is 9.765625MHz, and the PLL of the DAC is disabled.

jesd204B Configure L-M-F-S-Hd 1 TX 41121 Interp =1

Input rate 2500 (MSPS) fDAC Max 2500MSPS

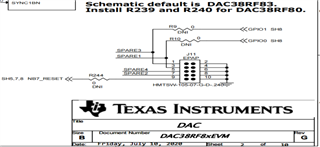

DAC38RF82EVM R9 and R10 are shorted, and GPO0 and GPO1 are enabled in the register, as shown in the following figure

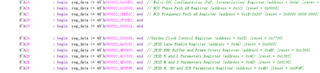

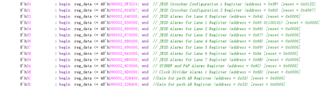

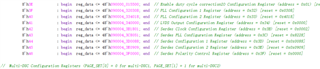

The DAC register settings are as follows:

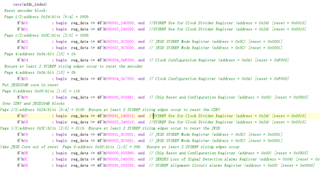

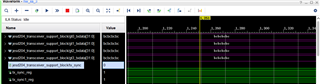

The following figure shows the link establishment sequence

The process of link establishment is as follows:

1. Initialize the FPGA (XCKU060-2FFVA1156I) jesd204B IP core;

2. reset DAC uses SW1 on the DAC38RF82EVM;

3. Initialize the DAC registers.