Hi, team:

I have some question about TSC2004 test mode 0, could you help explain it:

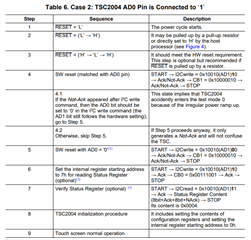

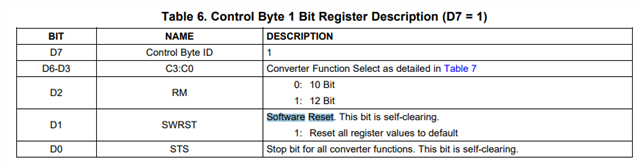

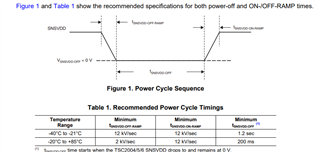

1. I know if the power on slope not satisfied requirement will enter test mode, I want to know more detail what is the concrete power-on slope will enter, and how to judge the test mode.

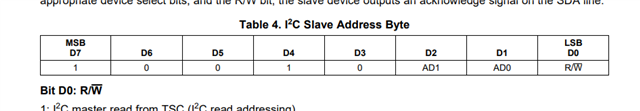

2. In the table below, I can see that if I enter test mode, AD0 will be set to 0, and if I identify the device with the address of ad0=0, the chip will exit test mode, right?