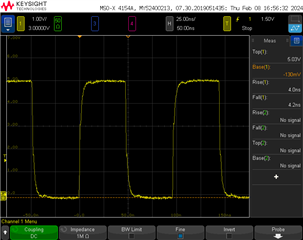

How tolerant is the SPI interface to nonmonotonicities? Is there a deglitch filter on the SCLK/CS/MOSI lines? I am seeing nonmonotonicities of up to 100mV and 0.5ns to 1ns on signal edges into the ADC, would these negatively affect the SPI communication?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.