Hello,

we're going to design a system with an ADS5296A chip and use it in a single chip, multiple channel (non-interleaved) configuration.

By looking at the datasheet, however, is not crystal clear how we should drive the SYNC signal for a proper synchronization of the decimators (that will be used in a 2x decimation configuration) on each channel.

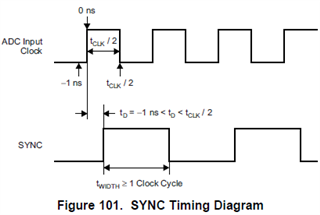

From the above picture, it looks that one should drive the SYNC signal as a divided version of the clock, with the division factor equal to the decimation factor. For example, if decimation is 2x, then the SYNC is a square wave with half of the frequency of the ADC input clock. However, just above this image, the datasheet is referring to the SYNC signal as a "pulse", not a series of pulses.

Thus our question: in order to ensure proper channel synchronization, must the SYNC signal be driven as a square wave/series of pulses, or is it enough to have a single pulse after which the decimators will always be aligned?

Thanks for your time.

Best regards,

Stefano