Hello team,

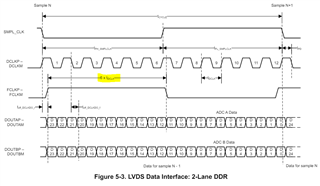

On the datasheet Fig 5-3, FCLK is 6*DCLK, when data frame width =24bit (DDR).

What would be the length of FCLK, when data frame width =20bit (DDR)?

Is it going to be 5*DCLK?

Best Regards,

Kei Kuwahara

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello team,

On the datasheet Fig 5-3, FCLK is 6*DCLK, when data frame width =24bit (DDR).

What would be the length of FCLK, when data frame width =20bit (DDR)?

Is it going to be 5*DCLK?

Best Regards,

Kei Kuwahara

Hello team,

Can anyone answer to my question?

Best Regards,

Kei Kuwahara

Hi Kuwahara-san,

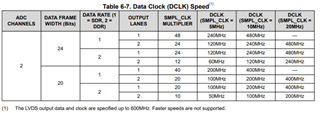

Thanks for your patience. I believe when the data frame width is changed to 20 bits, FCLK will still be 6*DCLK in 2-lane DDR mode but the DCLK frequency will change as shown in section 6.3.8:

Best regards,

Samiha