Tool/software:

Hi, everyone.

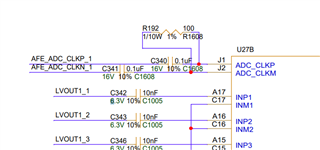

I am developing a medical ultrasound system using the AFE5816 device. I need to digitize the received signals using the AFE5816, and I have a question regarding the clock requirements stated in the datasheet.

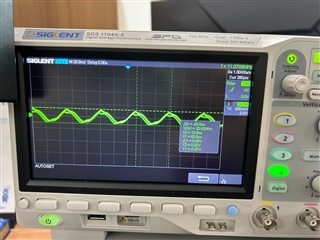

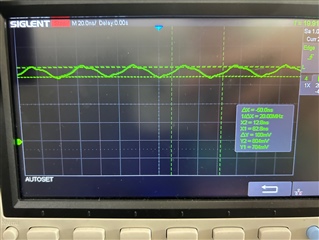

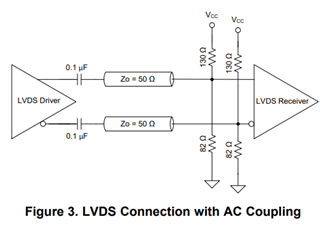

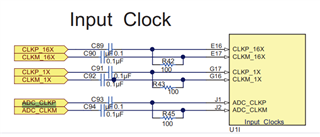

I plan to use LVDS or LVPECL, and the clock requirements mention a Vpp value when AC-coupled, while the common mode voltage is internally set to 1V. The clock provided by my board is as shown in the image below. Even though the Vpp is satisfied, could there be an issue because it is not AC-coupled?

And, Can you tell me minimum value of Vpp for normal opertaion in LVDS and LVCEPL?

In datasheet, there is a typical value only.

Thank you