Tool/software:

Hi team,

I received some questions about ADS8671 from customer. Please support.

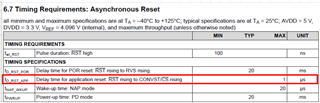

1) Datasheet parameter tD_RST_APP is speced 1us max. Does it mean CONVST/CS must be toggled Low to High within 1us after the rising edge of RST for proper reset operation?

Is it okay that we toggle CONVST/CS together with RST or earlier than RST?

2) Customer is going to use this device like below diagram. It repeats short Low pulse for conversion trigger(SCLK stay low) and Output data read(SCLK has only 8 cycles to read out 14bit data by Dual SDO-x mode).

What is the minimum pulse width for CS?

If the High period after the short pulse is enough longer than tconv, customer can read out ADC Data(N), ADC Data(N+2) as their expectation. Is it correct?

Best Regards,