Tool/software:

I'm using the DAC82002 and am interested in achieving the maximum update rate possible. It appears to be only ~780 ksps (or maybe 500 ksps) per channel rather than 1 Msps and I want to confirm.

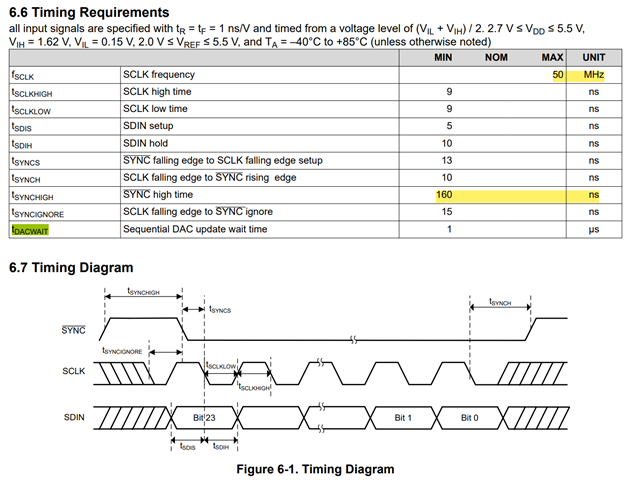

Per the datasheet, the maximum SPI rate is 50 MHz. Each transaction is 24 bits. So to update DAC-A output, it takes 24 bits, and to update DACB output, it takes a separate transaction of 24 bits. Between transactions, the !SYNC line must be high for 160 ns.

So the minimum time required to update a single register is 24 bits at 50 MHz (480 ns) plus the required !SYNC idle high time (160 ns) for a total of 640 ns.

(0 ns): update DAC-A

(0.640 us) update DAC-B

(1.2 us) update DAC-A

(1.84 us) update DAC-B

etc...

Or, am I misinterpreting the datasheet and is t_DACWAIT the duration one must wait between any transaction, not just a per-channel wait. This would limit the update rate to 500 ksps per channel.

(0 us): update DAC-A

(1 us) update DAC-B

(2 us) update DAC-A

(3 us) update DAC-B

etc...