Tool/software:

hello TI,

we have loop powered HART device working nicely once it gets powered up successfully.

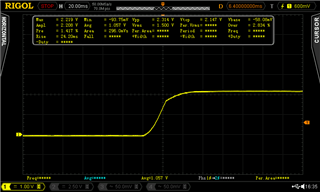

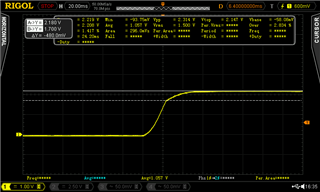

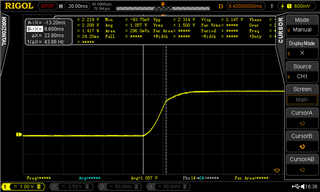

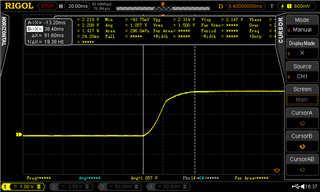

BUT we've found that DAC8740H modem something locks during power up.

what is the rush current needed for DAC8740H to ensure correct power up every time?

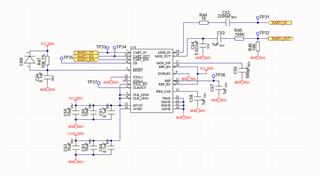

we use DAC8740H in circuit as suggested in its datasheet. we just limit its 3.3V power supply total current to 3mA.

would you have some suggestions to lower the DAC78740H rush current?

thank you in advance.

best regards,

david_r