Other Parts Discussed in Thread: ADS1298

Tool/software:

TI Engineer

Hello!

I have the following 3 questions to ask:

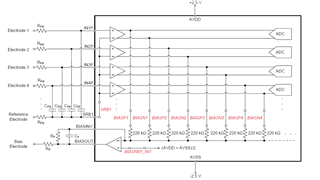

1. According to the diagram below, I will connect the N end as a reference. Does the N end pin of the chip need to be externally connected to AVDD?

2. Connect two chips in a daisy-chain configuration. Do the SRB1 pins on both chips need to be connected together? Refer to the diagram for problem 1 for the channel connection between the two chips.

3.If the bias bias drive is shared by both chips using the first chip's bias output, does the second chip's biasout and biasin pins not need to be connected, and only the biasin pin of the second chip needs to be connected to the biasin pin of the first chip?

I would appreciate your reply!

Thank you!