Tool/software:

Dear Team,

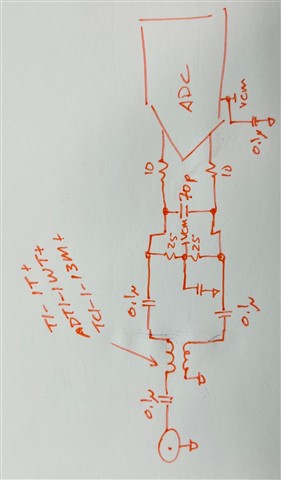

We are planning to use ADC16DV160 with transformer coupled front end design. We got S1P file for ADC from TI query.

But we are having issues during ADC simulation load impedance port assignment. ADC16DV160 have P & N pair signals for one channel but we only have one S1P file.

Q1) Can you confirm that this S1P file values obtained for ADC-(P or N) channel alone (or) ADC Total input impedance across P & N pins?

Q2) How to connect out front end circuit with ADC'S S-Parameter file?

Q3) Can you provide proper method for ADS simulation for ADC16DV160 termination?

We attached reference circuit for Reference.

Regards,

Esakki.