Other Parts Discussed in Thread: OPA1652, OPA1602, , BUF634, TINA-TI, OPA1612, OPA1656, OPA1642, DAC11001B

Tool/software:

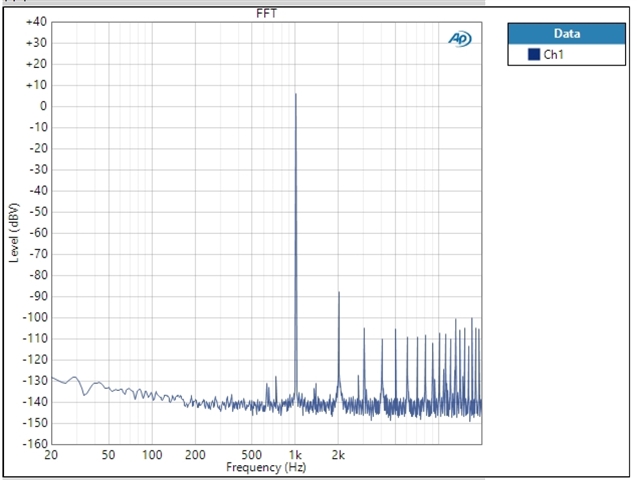

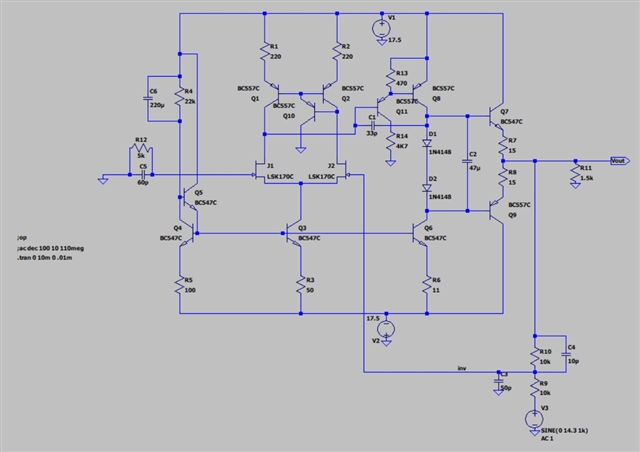

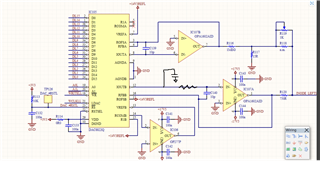

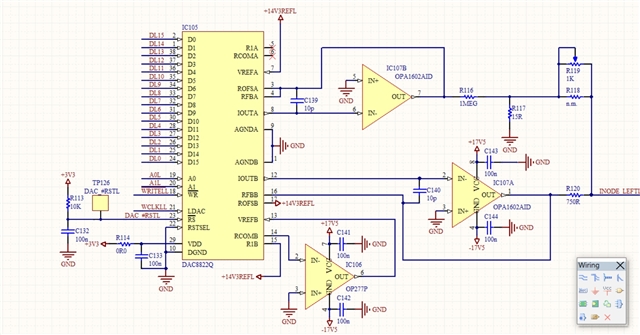

Hello, I'm using the DAC 8822 for a high resolution audio application as in the attached schematic. The 8822 is driven by an FPGA and the output of the circuit in the attached schematic is connected to the inverting input of an opamp used as inverting summer. While I reached the goals in terms of resolution, sampling frequency and SNR, the THD+N is much higher than expected. Please note that I minimized the major zero-crossing glitch by an auxiliary circuit, residual glitch spurious are well below the THD harmonics.

One cause I found for the excess THD was the limited GBW of the opamp initially used as I/V converter out of the 8822 (OPA1652). After replacing it with an OPA1602, I got a 6dB reduction of the THD. In order to check for need for further GBW, I reduced the VREF value, expecting even further THD reduction, but this didn't happen, therefore I guess the OPA1602 is ok.

THD @ 0dBFS out of the DAC circuit is now 0.002%, my goal is about 20dB less. The strange thing is that the THD out of IC107A ("coarse" DAC) is exactally same. I was expecting that the second DAC ("fine" DAC), which I use to "refine" the waveform of the first DAC (which works, as when I check the waveform @ -91dB, I still see a nice sinewave with 1% THD+N instead of a gross 1-LSBpp squarewave), helped to keep THD lower, but this doesn't happen.

Therefore I think the problem is mainly related to the first DAC. Is there any practical way to reduce the first ("gross") DAC THD? Is this related to some parameter like bipolar zero error, full-scale error or the like?

Thank you for your help.