Tool/software:

Hello,

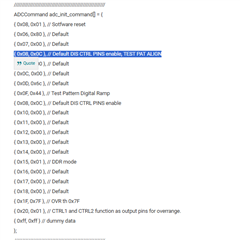

Can someone please help me understand about the TEST PAT ALIGN field in register 8 of ADS42LB69?

As I understand it, writing 1 to the TEST PAT ALIGN field will synchronize the phase of the test pattern of channel A and channel B, so for example, if I select digital ramp as the test pattern, the same data will be output from the two channels.

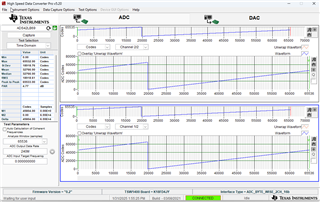

Unfortunately, the output data sequences are not actually in phase. I have confirmed that each channel is digital ramping independently.

Am I understanding something wrong?

Best Regards,

Keisuke