Other Parts Discussed in Thread: AMC131M03,

Tool/software:

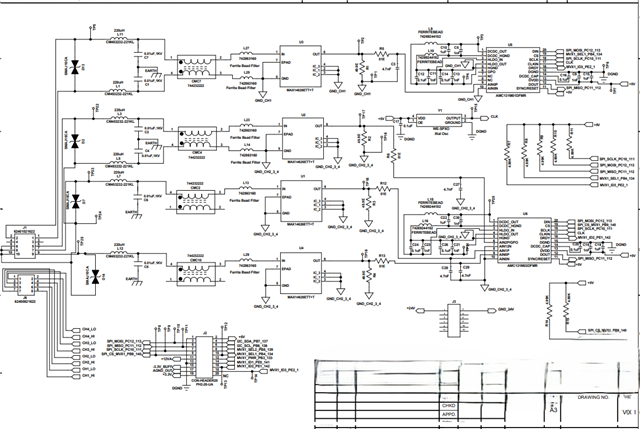

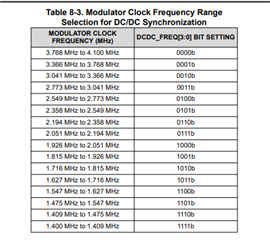

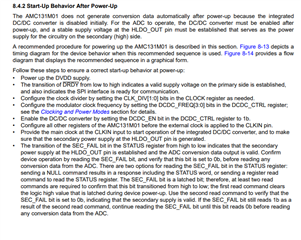

I am using an STM microcontroller to control the AMC131M01DFMR using SPI. I have enabled the DCDC bit, and the CIN frequency and divider are set to default. A continuous clock is provided at CIN after power-up. After that, write register and read register commands are sent for configuration, with only the DCDC bit enabled while keeping everything else at default. However, I am not getting any voltage at the DCDC output. What could be the possible reasons for this issue?