Tool/software:

Hello

We are using the DAC38J82EVM and a KintexUS+ board through FMC connection to create a JESD204B system. We use the TI204C-IP from TI.

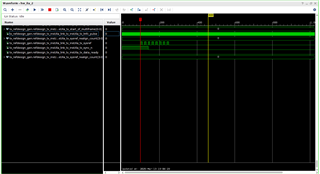

Once the DAC is initialized through DAC38J82EVM GUI, we get the sync assertion to the FPGA from DAC. Assuming the FPGA sends required /K/ in all 8 lanes, we expect the DAC to de-assert sync as per the specification's subclass 1 operation. However this never happens. The DAC38J82EVM GUI does not show any alarms either. Please see the ILA waves attached.

We verified the sedes by using an ibert core in FPGA to generate various random test patterns and verifying them in the DAC side and it works fine.

Can this be due to a sysref signal timing issue? As the device clock for FPGA, we use the clock12 from EVM (LMK0482x) and as the sysref for FPGA we use sclock1 from EVM(LMK0482x). These are not from the same group of the clock generator chip. We had to do this due to a limitation in wiring of the FMC connector to FPGA pins.

If this is not due to a sysref issue, the only possibility for this to happen may be that TI204C-IP not sending the /K/ sequences. What could cause this? We have double checked the configurations and connections of the ip core.

Also, are there any debugging methods that we can use to see the activity of the serial lines?

Thanks

A