Other Parts Discussed in Thread: LMK04828, TSW14J58EVM, , TSW14J57EVM, TSW14J59EVM

Tool/software:

Dear Technical Support Team,

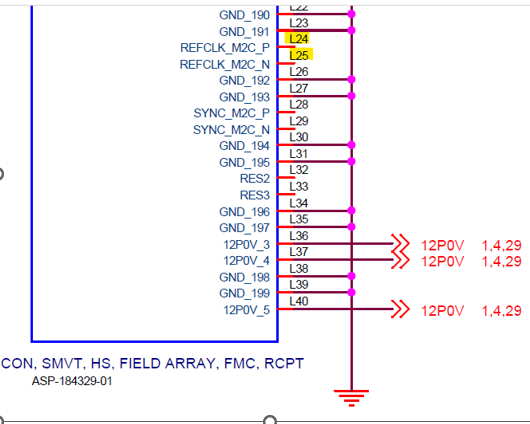

The FPGA_CLKA_FMC_N output(LMK04828) from the ADC12DJ5200RFEVM is input to L25 of the TSW14J58EVM, but in Rev. A, L25 is connected to GND.

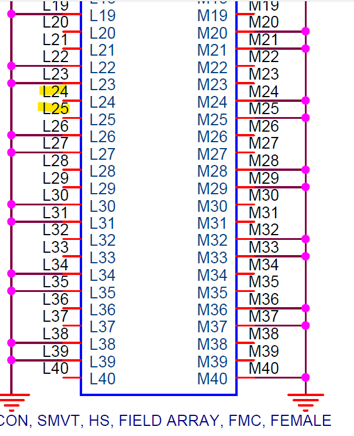

Also, L24 and L25 seem to be unconnected for TSW14J57EVM and TSW14J59EVM.

Q1

Am I correct in recognizing that FPGA_CLKA_FMC_P and N from ADC12DJ5200RFEVM are not used especially in TSW?

Q2

My board silk has DC182_A10. Dose it mean Rev.A. Is it work with ADC12DJ5200RFEVM ?

According to this E2E, there is Rev.C board for TSW14J58EVM

Best Regards,

ttd

■TSW14J57EVM

■TSW14J59EVM