Tool/software:

Dear Team,

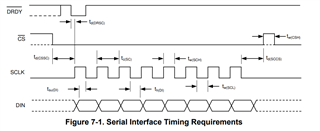

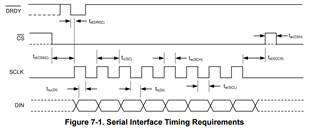

I've a question about the SPI timing of the ADS1262 device. The datasheet of the ADC says (Pg 10) that the delay time td(CSSC) from CS falling edge and first SCLK rising edge shall be 50 ns. But the sampling SCLK edge is the falling edge. The SCLK period requirement is 125 ns minimum. Does anyone know if reducing the delay time from 50ns to 0 ns, but increasing the period used to 1 us would work too or would have some problems? What is the real reason of the 50 ns requirement?

Regards

Tiziano