Part Number: ADS1251

Other Parts Discussed in Thread: ADS127L11

Tool/software:

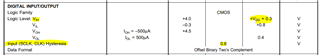

The datasheet states that the nominal CLK and SCLK input voltage is 0.6V, but doesn't specify a min or max allowable. If I had a microcontroller deviate from normal configuration and apply VCC/logic high to the clock pin instead of an ~0.6V amplitude clock signal, will this cause damage to either of the CLK or SCLK pins?