Other Parts Discussed in Thread: DAC8775

Tool/software:

Hi,

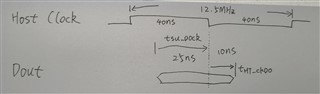

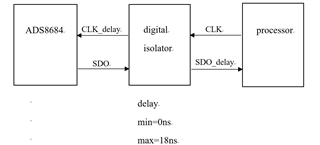

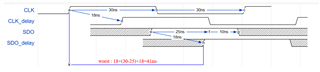

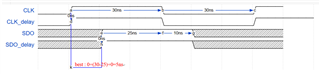

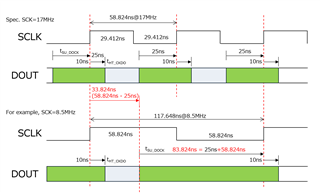

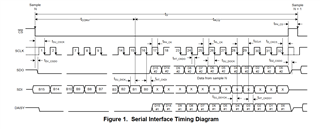

According to the ADS8684 datasheet, valid SDO width in the worst case is tHT_CKDO + tSU_DOCK = 10ns + 25ns = 35ns.

I understand that as the frequency of SCLK decreases, the valid SDO width will increase.

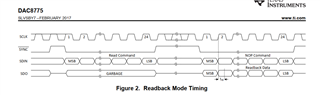

Is it possible to provide the time from SCLK rising edge to SDO valid like DAC8775 datasheet?

Thanks and best regards.