Tool/software:

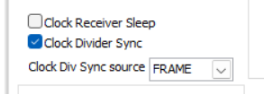

My system is working with 1250MHz Fdac, 312.5MHz Ffpga. I am generating 312.5 MSPS 20MHz sine signal from FPGA. LO frequency is 1GHz. I am in single sync source mode and NCO is off. I am using ZCU102 as FPGA.

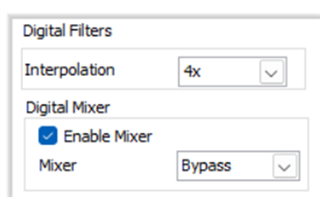

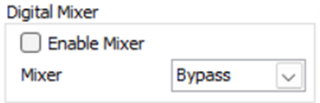

I have a question about digital mixer. I set the interpolation value to 4x to keep the sample size the same. I keep Digital Mixer in Bypass mode in Enable.

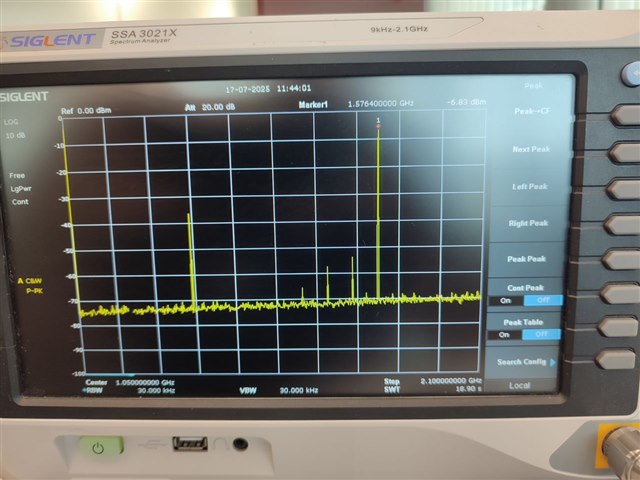

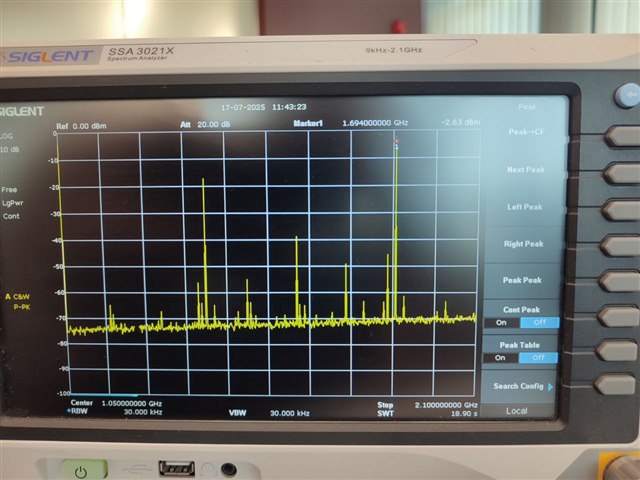

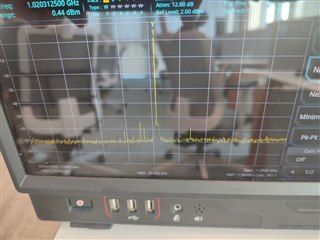

The spectrum view of these settings is as follows.

When I disable the Mixer from the GUI, I can receive my signal properly.

What is the reason for this and how can I fix it?

Also, another question I want to ask is that when the settings are “fDAC = 1.25GSPS, fOUT = 20MHz” I see 70dBc instead of 82dBc as SFDR value as mentioned at Datasheet. What could be the reason for this?