Tool/software:

Hi,

We are currently using five ADS7066IYBHT devices in a daisy chain configuration:

FPGA → ADC0 → ADC1 → ADC2 → ADC3 → ADC4 → FPGA

We are trying to write 0x80 or 0x8A to the GENERAL_CFG register (Address: 0x01) of each ADC to enable the internal reference and perform offset calibration.

The protocol used is SPI-00 (default), and the SCLK frequency is 1 MHz.

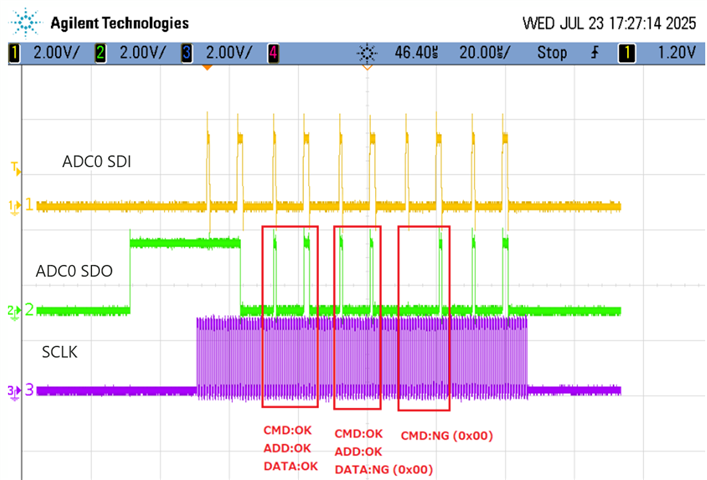

After sending the data 0x080180 (24-bit) from the FPGA to ADC0, the SDO output from ADC0 seems to show proper command/address/data timing. However, for ADC2, ADC3, and ADC4, the timing of the data output on SDO becomes misaligned, and the GENERAL_CFG register write does not succeed (the received command and data are 0x00).

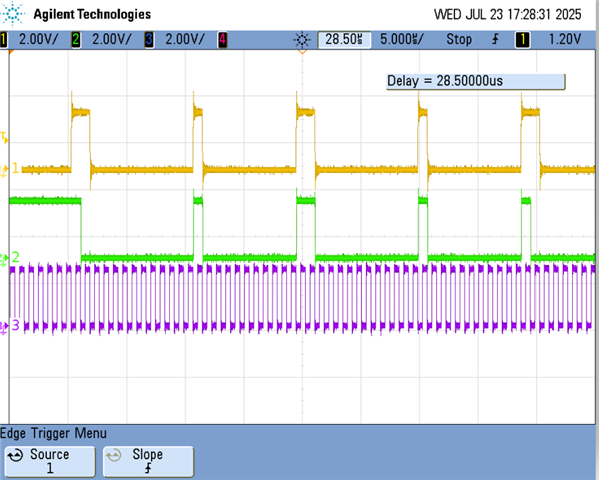

We have attached oscilloscope waveforms showing this issue.

We would like to confirm the following points:

① Regarding the SPI-00 protocol timing

Is it correct that in SPI-00 mode, the ADC latches SDI data on the rising edge of SCLK and updates the SDO data on the falling edge of SCLK?

② Regarding the register initialization

We are currently setting the following registers during ADC initialization:

-

GENERAL_CFG register (0x01) = 0x8A

→ GENERAL_CFG[1]: CAL = 1 (ADC offset calibration enabled)

→ Is it required to perform offset calibration as part of ADC initialization? -

OPMODE_CFG register (0x04) = 0x08

→ OPMODE_CFG[3:0]: CLK_DIV = 1000b (Sampling frequency = 62.5 kSPS)

If other registers must be configured to operate the ADC correctly in daisy chain mode, please let us know.

③ Hypothesis regarding the communication issue

We suspect that the issue may be caused by insufficient number of SCLK clocks when sending data to all 5 ADCs.

Since the chain consists of 5 devices, we believe that 24 bits × 5 = 120 bits of SCLK are required in a single SPI transmission to propagate data correctly through all devices.

However, we are currently sending 24-bit command/address/data (0x080180) sequentially 5 times, which may not be enough to allow the downstream ADCs to receive and pass on data via SDO.

④ Questions to confirm

-

Is it necessary to send 120 SCLK clocks in a single transmission when writing to 5 ADCs in daisy chain mode?

-

Alternatively, is it valid to send 5 sets of 24-bit commands separately, as long as additional SCLK clocks (24 × (N−1) = 96 bits) are sent after to allow data propagation through the chain?

-

Are there any other timing or configuration points that we should be aware of when operating ADS7066 in daisy chain mode?

We appreciate your confirmation and support.

Oscilloscope captures and circuit schematics are available upon request. Please let us know if you need further details.

Best regards,

Conor