Other Parts Discussed in Thread: ADS9813, ADS8688W

Tool/software:

Hi Team,

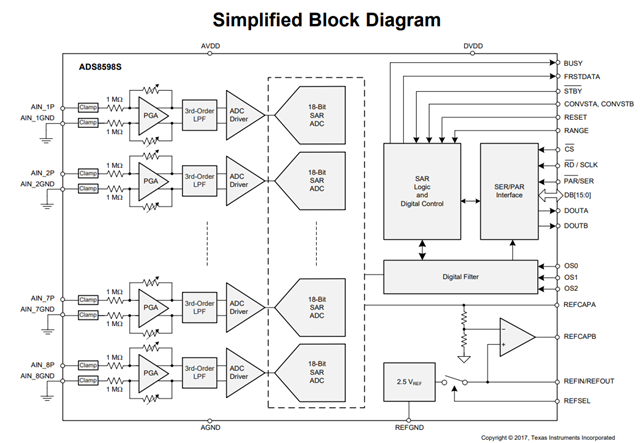

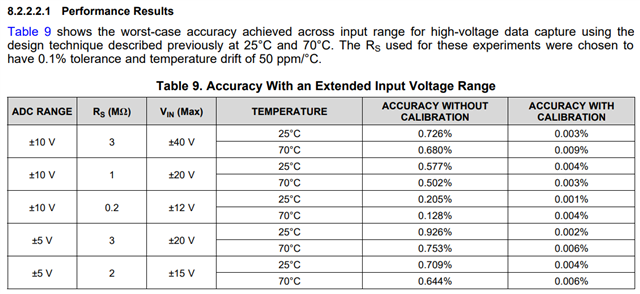

We are planning to use the ADS8598S ADC in the data acquisition system, and want to make sure to fulfill this requirement:

- The input voltage range for each channel has an upper bound of ± 50 V (100 VPP) and a lower bound of <= ± 1 V ( 2 VPP).

Could you please let us know how this requirement can be fulfilled to support both the upper and lower limits of the voltage?

Could you please let us know how this requirement can be fulfilled to support both the upper and lower limits of the voltage?

During our quick exploration, we found the PGA281 chipset. Maybe this can be useful for our requirement. Please confirm.

Let us know if this is the correct way to satisfy the above-mentioned requirement. Also, let us know if you have a better, cost-effective solution.

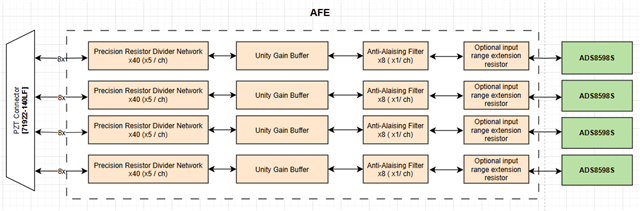

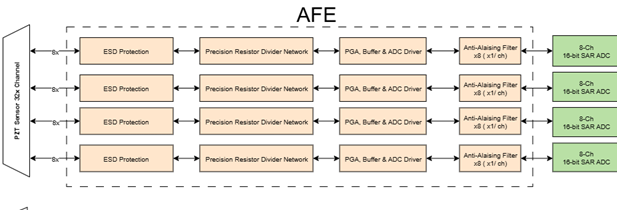

Attached is the basic architecture diagram for a more detailed understanding.

Thanks & Regards,

Sahil Nayak