Other Parts Discussed in Thread: TXU0101

Tool/software:

Hi

we have a custom board with the ADS1675 and we observe a strange issue: Sometimes two samples samples in the data stream is shifted. One sample is shifted left and the following is shifted right one bit. We are operating the ADS1675 with the following parameter:

- MCLK= 20 MHz

- Output data rate 2.5 MHz

- DRATE set to "101"

- LL_CONFIG = high

- FPATH = Low

We are reading the data using an FPGA and my first guess was that this must be a timing issue of the FPGA. After thorough investigation it turned out that the shifted data must be coming out of the ADC:

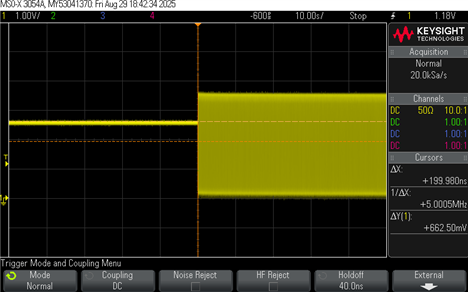

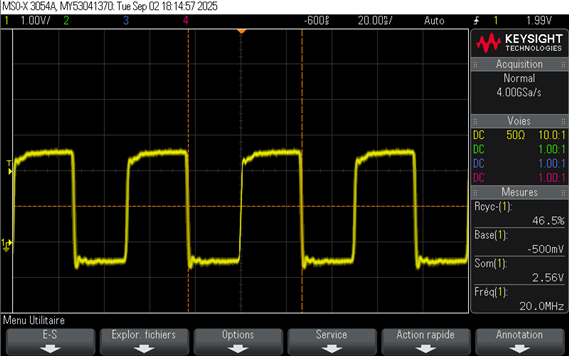

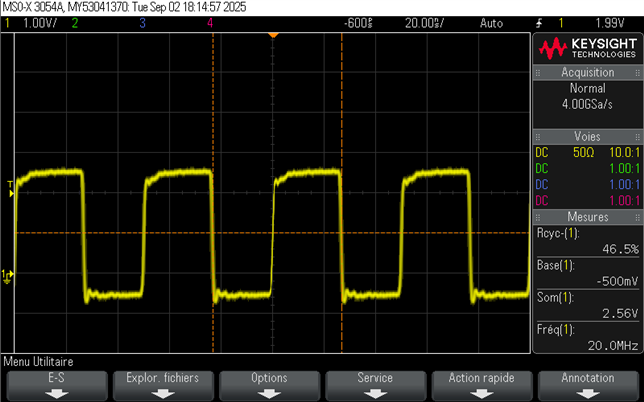

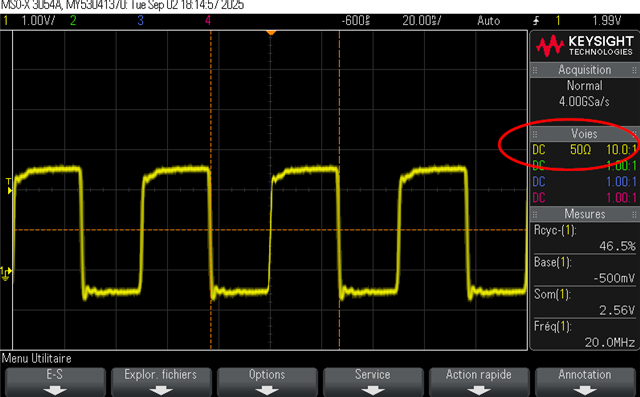

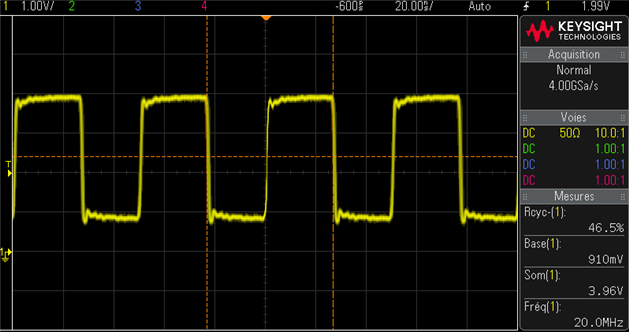

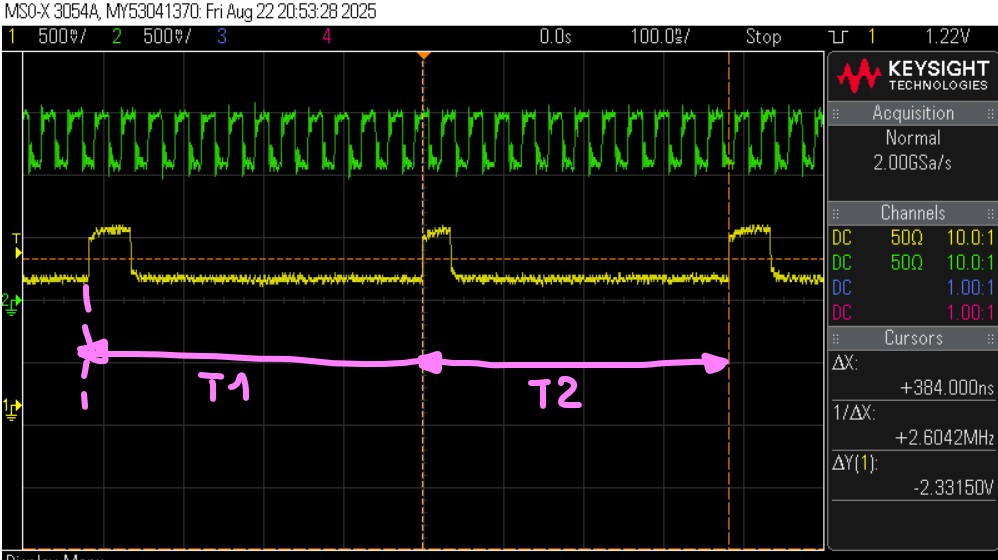

The green channel 2 is showing SCLK div 2 (Divided by a D-FF) and the yellow channel is the DRDY signal from the ADC. During normal operation the period between two DRDY pulses is 400 ns ( @ 2.5MHz ODR). The screenshot shows that there is a long period T1 = 416 ns with 25 clock edges followed by a short period of 384ns with 23 clock edges. This explains the two wrong samples, one shifted left, the other shifted right.

My question is now: What could cause the ADS16575 to behave like this ???

Kind regards

Reto