Hi,

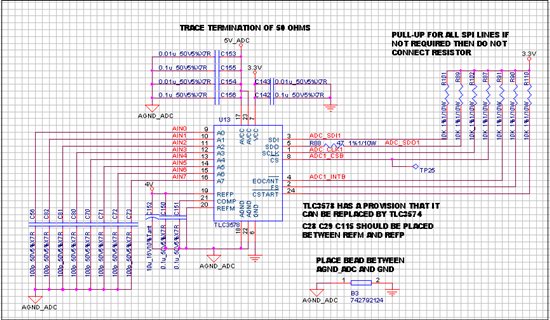

I am currently testing using the TLC3578IPW (TSSOP-24) on custom created board.

In this case i have pulled up the FS and CSTART as i dont have any dsp and all operations are to created using software

ref5040 is being used for 4v reference

i am testing this set up through a LPC1788 eval board

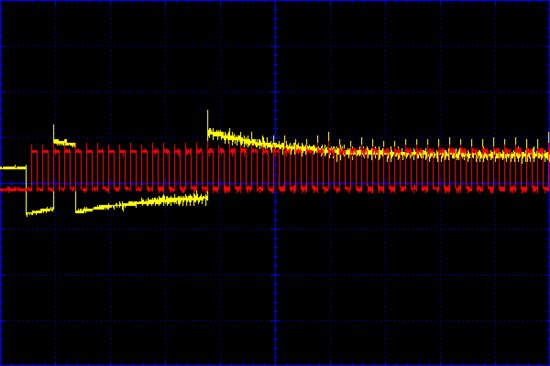

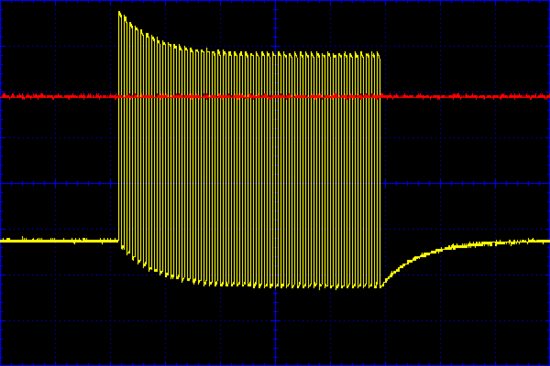

the spi clk is 100khz

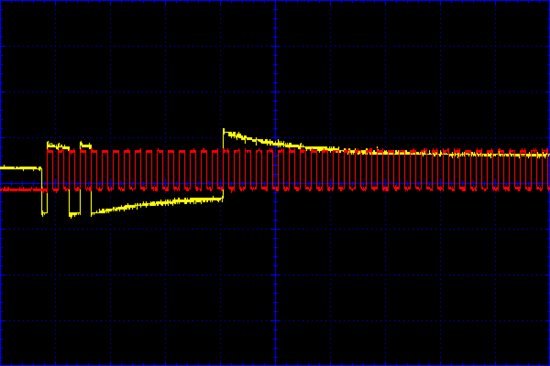

in the current process i am sending 0xA000 then 0xAA03

then i am reading channel 5 which i have by default given 5V i am reading the same using 0x5000 but my output data is 0xFFFF

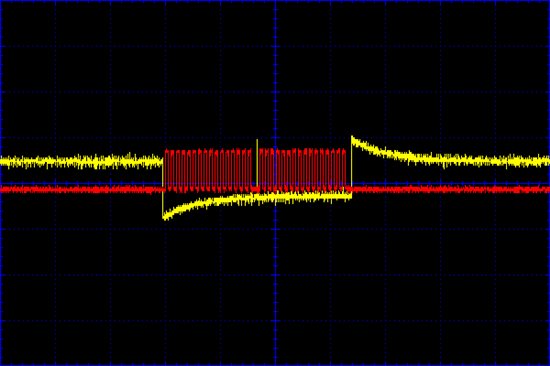

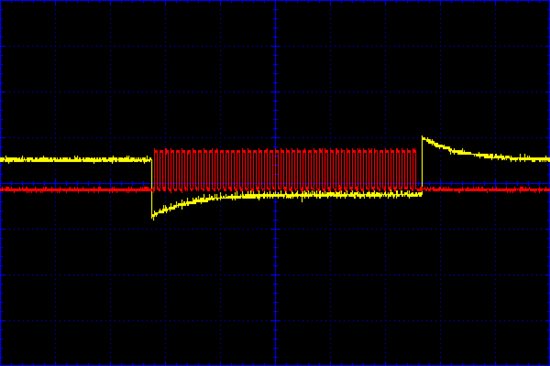

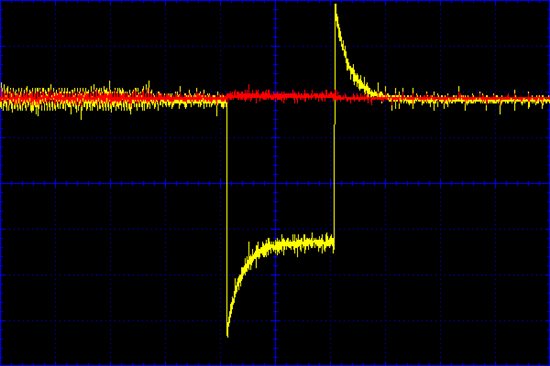

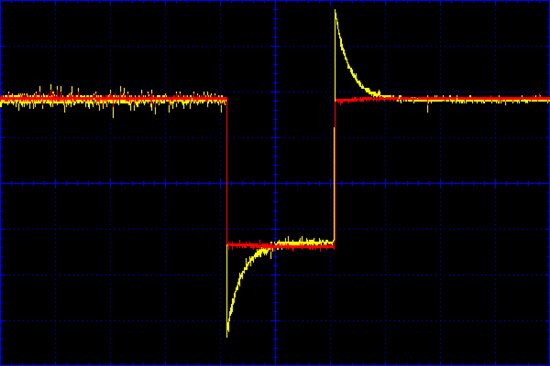

the INT and SDO line are always high when checked on the DSO for any operation

and i am not able to get any interrupt on the interrupt line

also i tried EOC mode but the INT is always high

is there any thing specific i am suppose to do which coding or any specific hardware changes.

Thanks Regards

Raquib Akolawala