I have some simple questions and report.

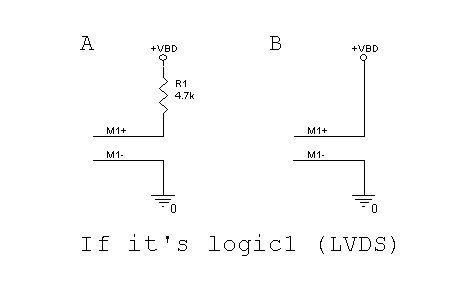

1. What exactly means that pulled up to +VBD in datasheet p#8, pin #30.

Is that figure like below? Which one is right?

2. Can I source CLK form Micro-Processor in the same way like pin #30 (related question #1)

3. In the document 'Using ADS8410/13 in Cascade Mode', Figure 3, Isn't the first ADC is a master according to LAT_Y/N connection.

4. In the document 'Using ADS8410/13 in Cascade Mode', Figure 15. Shouldn't I connect ADC3 CLK_O to CLK_O bus?