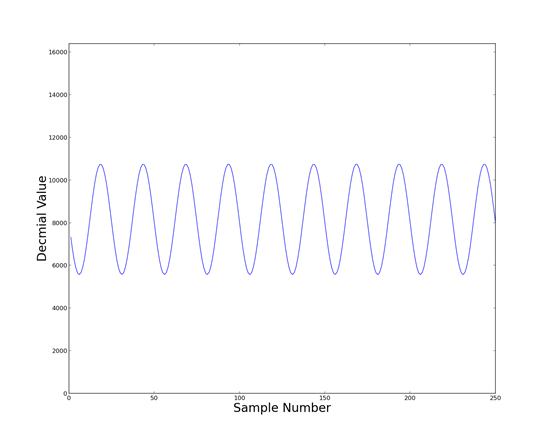

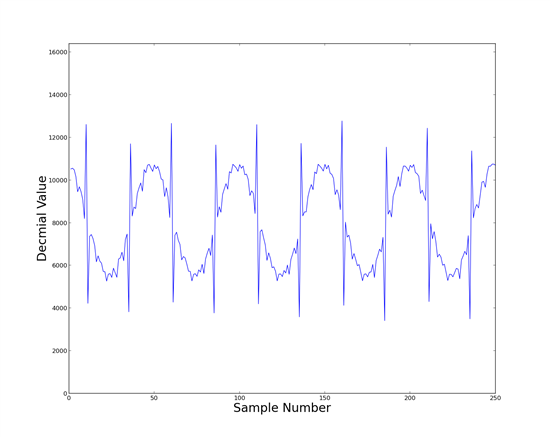

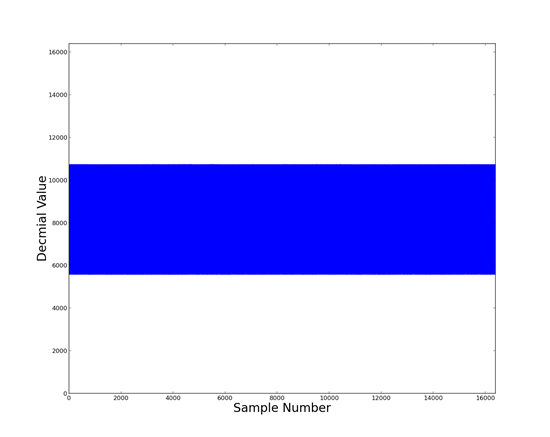

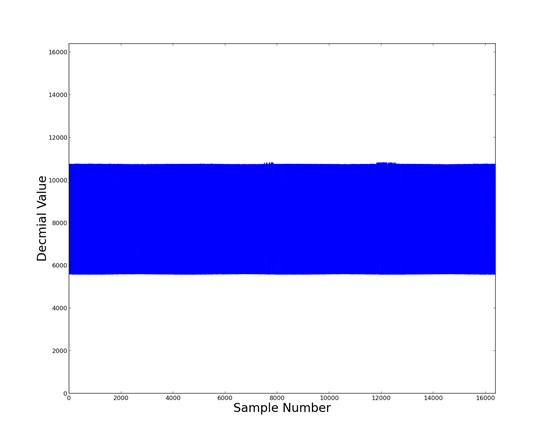

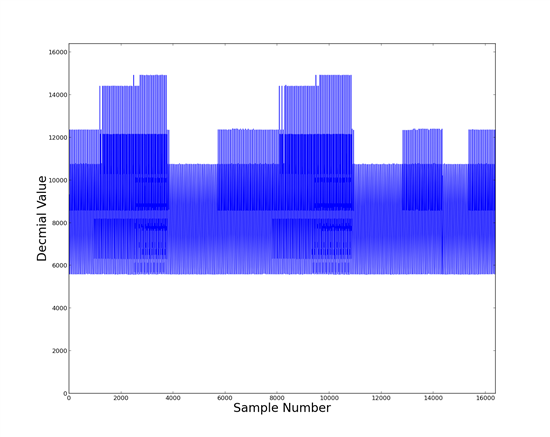

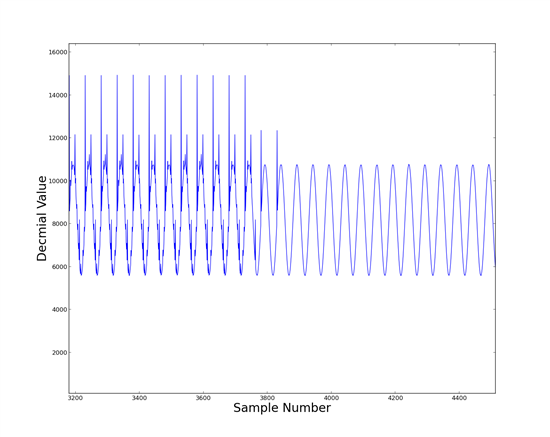

We are working with a ADS41B49 EVM and are trying to understand what is meant by a clocking speed of 250 MSPS. When we provide a 250 MHz clock the data from the ADC is very spiky and wrong. When we provide a 125 MHz clock the data from the ADC is exactly what we expect. I have tested and anything above 125 MHz (even 126 MHz) is problematic. If you would like some data to see for yourself I can send you some.

Thanks,

Kyle