Hi.

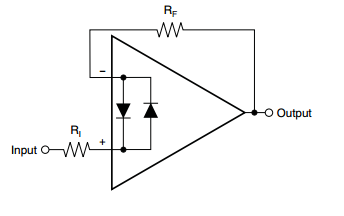

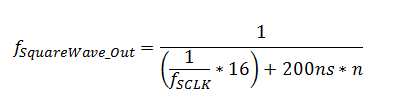

I am testing DAC8871 EVM with DXP tool. When using the square wave, it looks like the DAC is not meeting the slew rate parameter, mentioned in the data sheet 40V/us. Maybe I am missing something, could you help?. Attached are the files that describes the measured waveform, DXP configuration and DAC8871 EVM schematic diagram. The signal was measured in J1 connector, pin 2 and pin 6