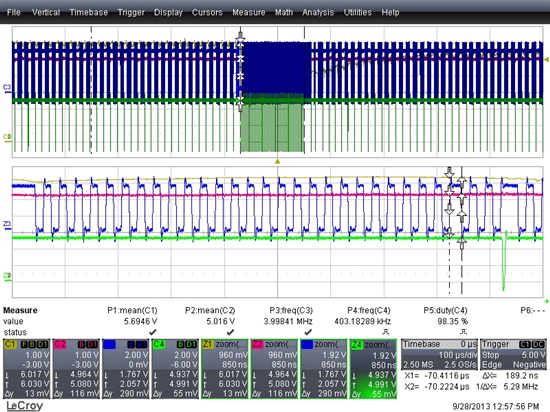

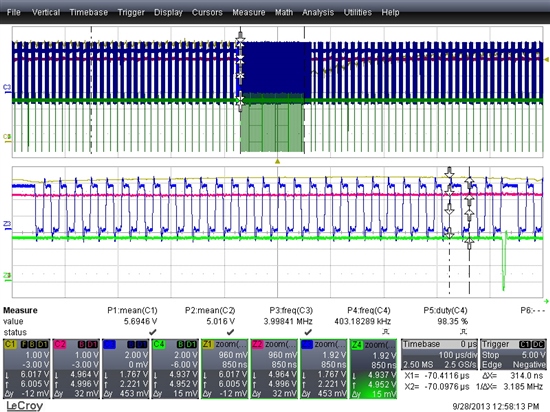

We are using ADS803E ADC in one of our products to convert analog voltage (varying from 0-5V) to digital data for the DSP TMS320VC5402. The ADC clock is derived from FPGA through inverter 74ACT04. During normal condition, the clock frequency is 4MHz and duty cycle 50%. During the fault condition, we have observed the clock frequency varying to 3.1MHz and pulse width varying to 180ns. Is the clock frequency / pulse width variation like the one observed below, will have any impact on the digital output data of the ADC? If there is any effect, then how to quantify the ADC output variation w.r.t. clock frquency/pulse width variation?

Attached are the waveforms depicting the clock pulse and ADC enable during the fault condition. Request your response asap. Thanks in advance.