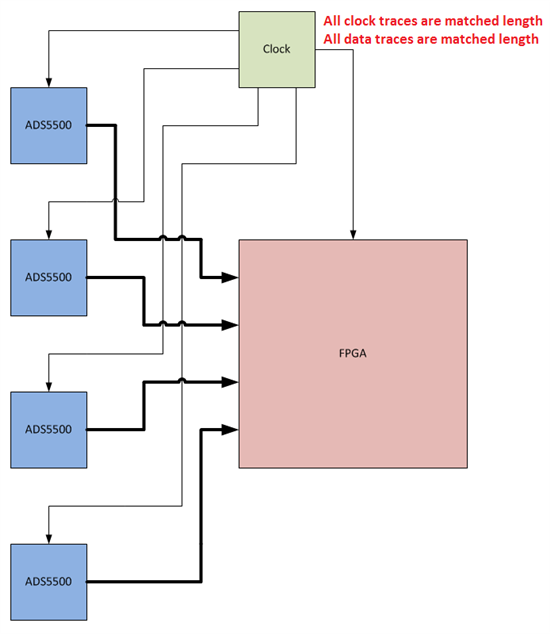

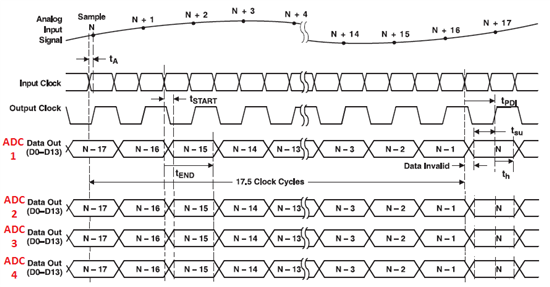

If I have two ADS5500 digitizers with DLL enabled both running off a common clock and measuring the same input signal will the relative phase of the two digital outputs have a fixed relationship from one power up to the next. There is an attached sketch showing the setup.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.