Hi

Our customer is planning to use DAC1280 in thier application.

We are confused with the signal connection from the Controller.

As described in this E2E post, we are confused about how to generate the

"SYNC" signal to the DAC1280.

Is the SYNC Signal necessary to control the DAC1280?

According to the Datasheet of DAC1280, it says

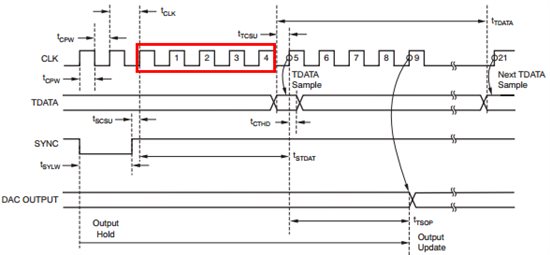

"When SYNC is taken high, the DAC resumes sampling TDATA on the sixth rising

CLK edge after SYNC is high"

So I think the data from the controller(MCU) should delay

first five clock cycles so that the DAC samples the TDATA Properly.

But it will be difficult from MCU to provide a clock delay.

Please let me know if there are any reference design connecting

DAC1280 with a MCU.

Best Regards.

Prad