Hi

I am interfacing the ADS54RF63EVM with the ML605 FPGA board. Glitches were seen when digitizing a sinusoidal input so I ended up having a look at the LVDS outputs and I see some strange behaviour as the sampling rate is increased.

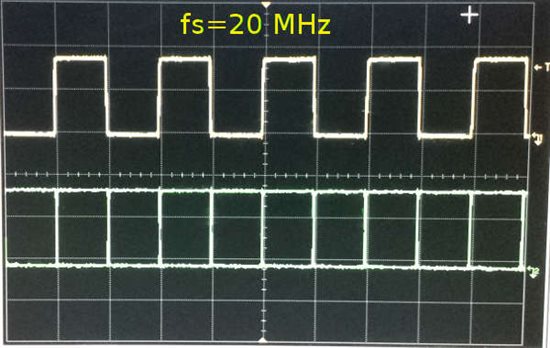

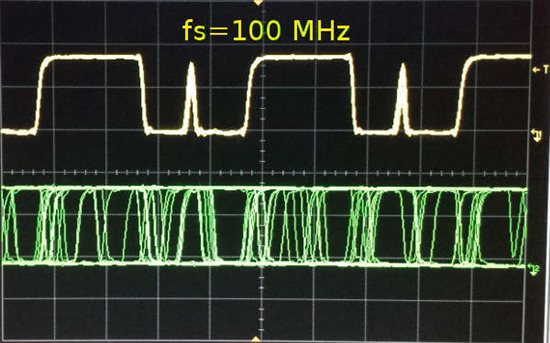

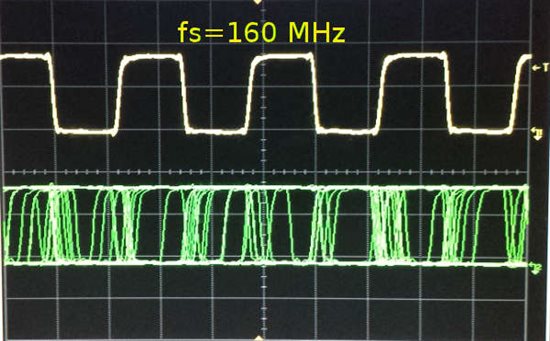

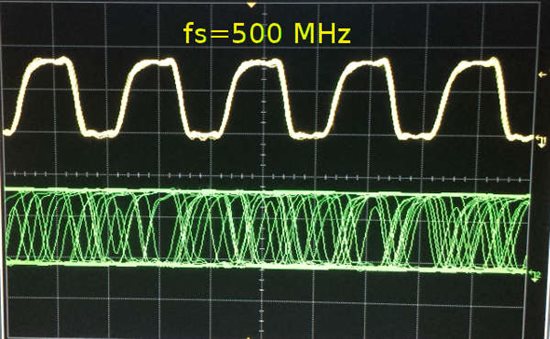

The oscilloscope screenshots below are for a 1.5 Vpp input clock and -1dBFS input sinusoid with frequency 15.5 mHz, just as the EVM user guide suggests. The top signal is the DRY output and the bottom is the LSB LVDS line, with some persistence. This is not what the datasheet suggests the output looks like and this is the second ADS54RF63EVM that we have tried showing this problem.

Can you suggest where the problem lies?