I would like to ask you basic questions about TLC7524 as below.

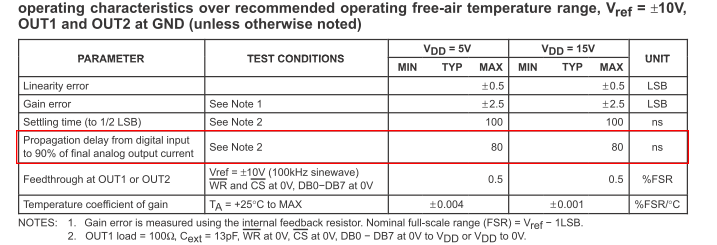

Q1) propagation delay timing

I do not understand well about the start timing of the delay. There describes the start timing is "digital input" on the datasheet.

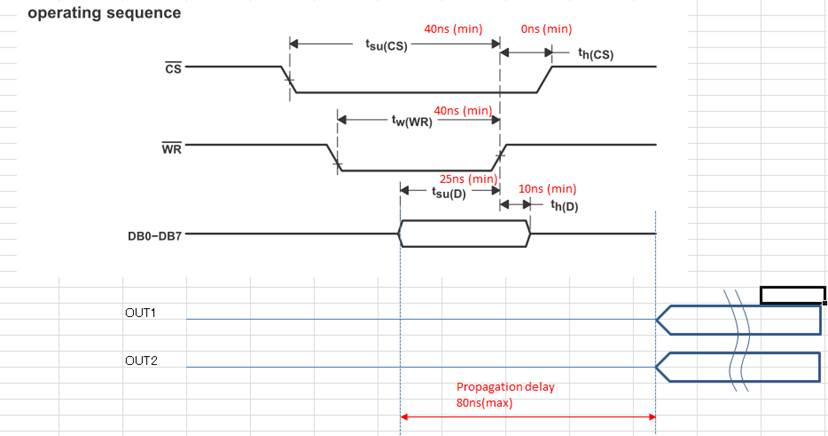

Does "digital input" mean the input of "DB0-DB7" data, right? (Please see below signal chart.)

Q2) In case of "CS=L and WR=L fixed using"

In case of both CS and WR = L(fixed), the output analog signal will be changed after 80ns(max, =propagation delay) when DB0-DB7 is cahnged. Is my understanding correct?

Q3) CS=L, WR=L, Data changing cycle is 100nSec

Does the device work correctly with above condition?

Thank you very much for your advice in advance.

Best Regards,