Hi,

I am planning to use two ADS8332 to sample a total of 16 single-ended channels and I have a few questions before I select the ADC.

- Sitara AM3357 will be used as the cpu

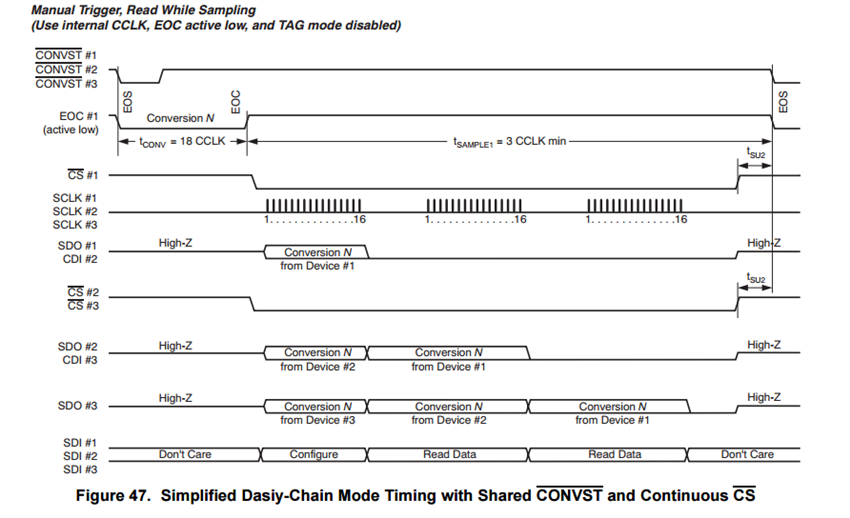

- The two ADCs will likely be on the same (dedicated) SPI bus. Likely wired in daisy chain mode

- I need at least a 10kHz sampling rate for all channels. A quick calculation shows this should be possible (500ksps/16ch = 31ksps/ch).

- The input channels will be driven by an instrumentation amplifier (PGA204, PGA206)

My questions are as such:

The Driver Amplifier Choice section of the ADS8332 datasheet shows an op-amp driving the ADC. Can I drive the ADC input using the output of the the instrumentation amplifiers (without the op-amp)?

How can I determine a realistic sampling rate for two devices? In Table 3, Auto-trigger mode takes 21CCLKs for each conversion. however, I am not sure how much overhead is required for the communication